UP009N10LT TOLTパッケージ-産業用に設計されたMOSFETです

産業用MOSFETの需要はますます高まっている。机械的ソリューションから、より厳しい適用条件まで、半導体メーカーは新しいパッケージの開発と技術改善を実施する必要があります。最初のto-252などの表面実装装置(SMD)から、最新のピンレス実装、内部シリコン技術の著しい改善に至るまで、MOSFETソリューションは産業市場の新たな要求に対応するために進化し続けています。ここでは,UOEのTOLT実装方式と熱性能,基板の信頼性について説明します。

主要な特徴主な利点と応用例です

重要な特性です

*超低RDS (on)です

* 300A以上の高定格電流です

*上部からの放熱です

*マイナスピン本体高差です

*無錫放熱パッドです

主な利点です:

*システム効率が良く、バッテリー寿命が延びます。

*高出力密度です

*優れた熱性能、省熱システムです。

*ヒートシンクへの熱抵抗を最小限に抑えます

重要な応用です:

移動ロボットです

*ドローンです

*軽電気自動車です

電動トラックです

*電動自転車です

電動工具です

バッテリー管理システムです

ターゲットとするアプリ市場です

UOEのTOLTパッケージの電力MOSFETは,非常に高い電力レベルを実現するのに役立ちます。トップ冷却により熱抵抗を改善したため、TOLTはデバイス数やシステムサイズを増やすことなく、高い電力が必要なアプリケーションに対応できます。そのため、TOLTパッケージの主な用途は大電流アプリケーションです。このパッケージは,出力レベル50 kWまでの大出力モータ・ドライバーに適しています。

パッケージ設計です

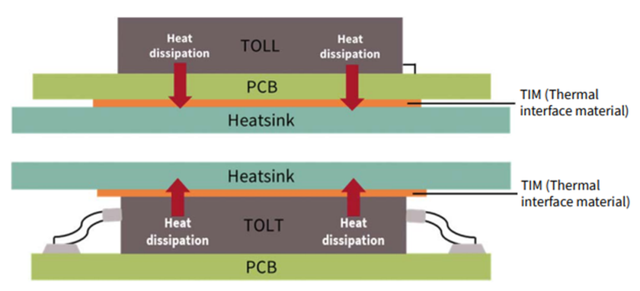

新しいTOLTパッケージのコンセプトは,標準の下部放熱電力MOSFETとは異なります。TOLTでは、パッケージ内のワイヤフレームが逆になり、ドレイン溶接パッド(チップ底部=ドレイン接続)がパッケージ上部に露出します。

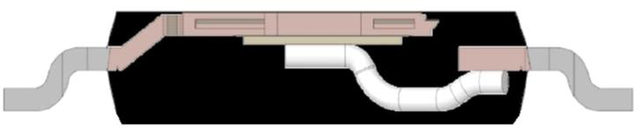

【図1】トルトの側面図です

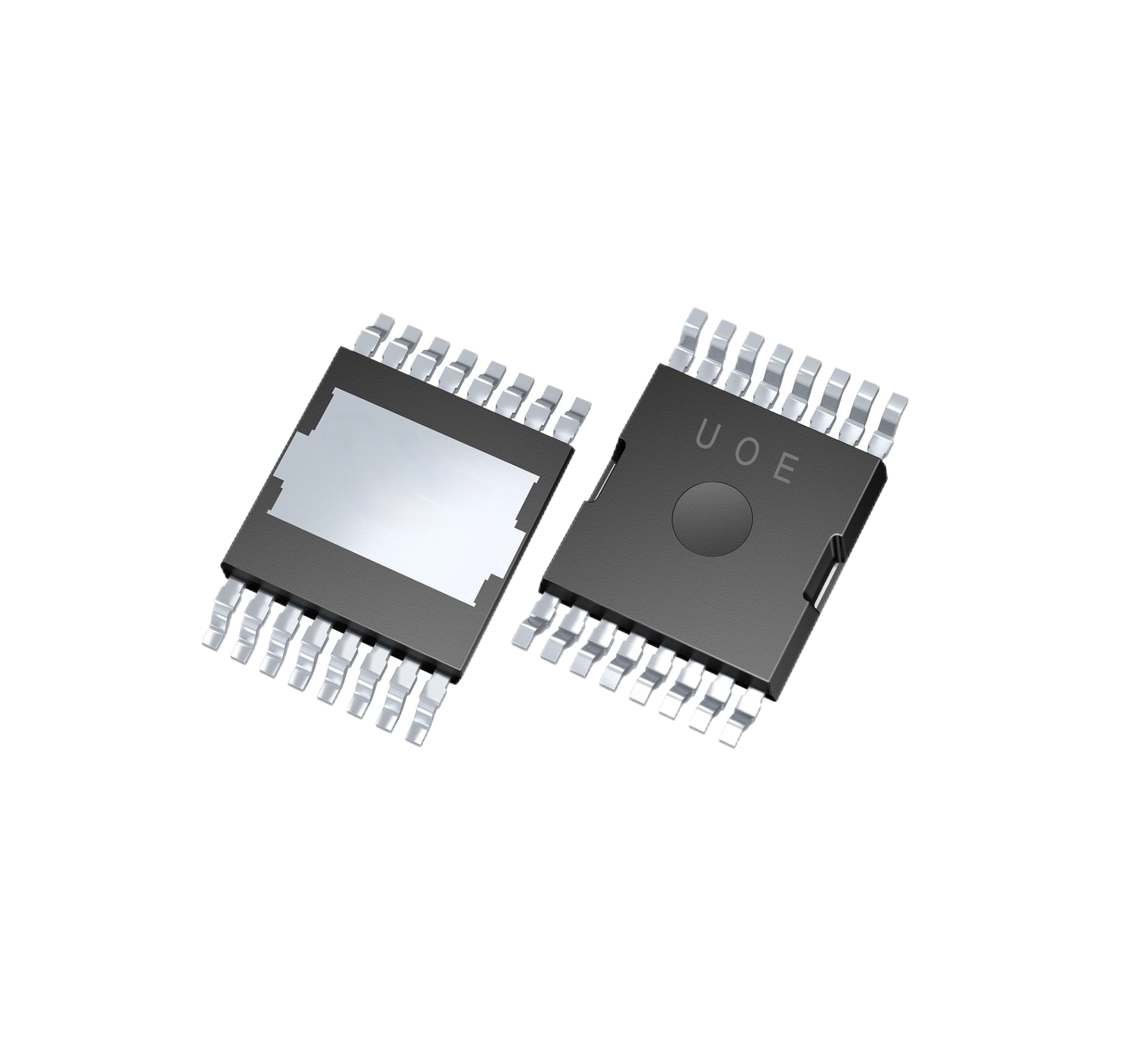

図2パッケージ外形図です

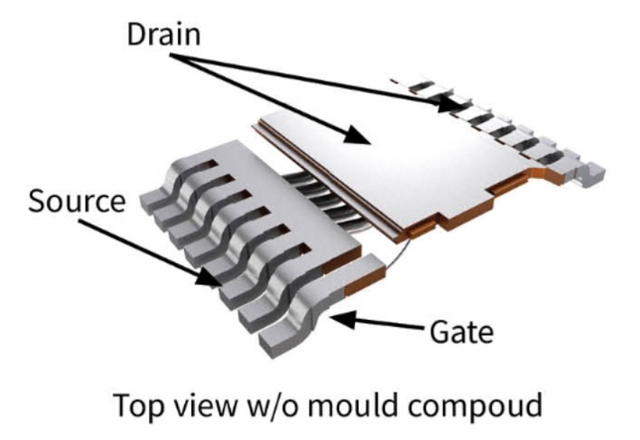

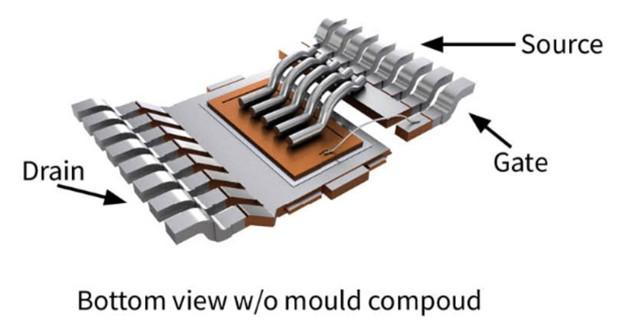

図3および図4は、ゲート、ソースおよびドレインのピンを示す。8つのピンをトップのむき出しのパッドに接続して、基板とドレイン接続します。パッケージの反対側の1ピンはゲート制御用で、残りの7ピンは電流ソースに接続されています。

【図3】TOLTの3 d画像です

図4 TOLTの底面図です

TOLTの強みとルールです

1、上部放熱だけでなく、アプリケーションのより高いパワーを得ることができますが、他のいくつかの重要な利点があります。標準的な放熱方式(図6)では、ラジエータは通常PCBの下に取り付けられます。このソリューションの欠点は、PCBとTIM/熱伝導性ペーストのパラメータに依存して熱性能が低下することです。これらの部品の熱伝導性の悪さは過熱と適用電力の低下を招き、より高い放熱コストを必要とする可能性があります。さらに、組み立て板はより高い温度に耐える必要があり、より高価なPCBを使用する必要があります。

図5裏面放熱方式のヒートパスです

2 . SMDコンポーネントは、使用可能面積を最適化するために、PCB下部のTOLT MOSFETの下(図10)に配置することができます。

【図6】TOLL & TOLTの放熱図です

3 . TOLTは電流/電力処理能力を高め、TOLLパッケージに比べてRthJAは20%低減、RthJCは50%改善、Rth(j-heatsink)は36%低減しました。

4です。追加の利点です

TOLT製品には,放熱システムの電力密度の向上やコスト削減以外にも利点があります。以下はいくつかの例です。

●PCBの下にラジエータが搭載されておらず、MOSFETの底側を通って熱が回路基板に伝わらないため、ゲートドライブやキャパシタをPCBの反対側に置くことができます。このような解決策はPCB空間をより有効に利用することができます。

●接地距離(ソースとドレイン電位の間の距離)を伸ばします。

●ガラス化転移温度の低いPCBを使用できます。

●PCBや近くの部品に伝わる熱が少なくなります。

5です。熱界面材料の厚さです

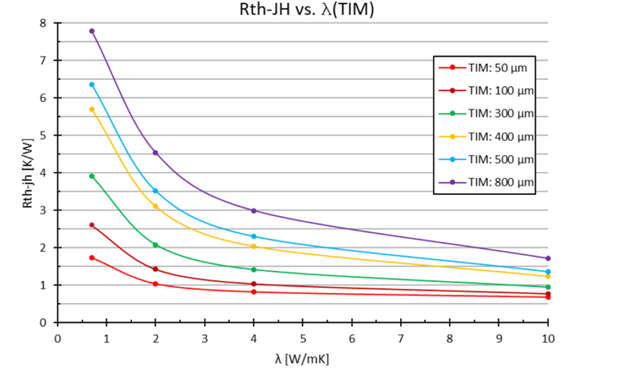

TOLTパッケージの熱性能を最適化し、パッケージの熱抵抗を可能な限り低くするためには、TIM厚さの最適化が重要となります。以下はTOLTパッケージのいくつかの異なるTIM厚さの状況をシミュレーションした図で、結び目からヒートシンクまでの合計RTHへの影響を分析します。シミュレーションでは、ヒートシンクの温度は周囲温度85°Cに固定します。

【図7】異なるTIM厚さに対するRthのTIM熱伝導率の相関を示す図です。

TIMが薄いほど熱抵抗が低いことがわかりますただし、TIMの熱伝導率(λ)値に注意すべきである。より良い熱伝導率はTIMの厚さの悪影響を補償します

市場に出回っている既存のTIMの熱伝導率は、通常3 ~ 6 W/mKの間です。最適な熱性能と十分な電気的遮蔽のバランスを達成するために、システムエンジニアはTIMの厚さと熱パラメータを最適化する必要があります。

顧客が最もよく使用し、市場で広く使用されている材料は熱伝導率が3 ~ 4 W/mKの範囲内のTIMです。この値のシミュレーションによると、MOSFET結び目とヒートシンクの間の熱抵抗は、特にTIMの厚さに応じて0.8と3K/Wの間で変化します。実際のTIM厚さが300 ~ 500 μmの場合、熱抵抗値は1.5 ~ 2.4K/Wになります。Rthが2.4 K/Wに等しく、MOSFET結び目とハウジングとの温度差が90°Cである場合(Tcase = 85°C、Tjmax = 175°Cとする)、単一のTOLT MOSFETは約40 Wの電力を消費します。

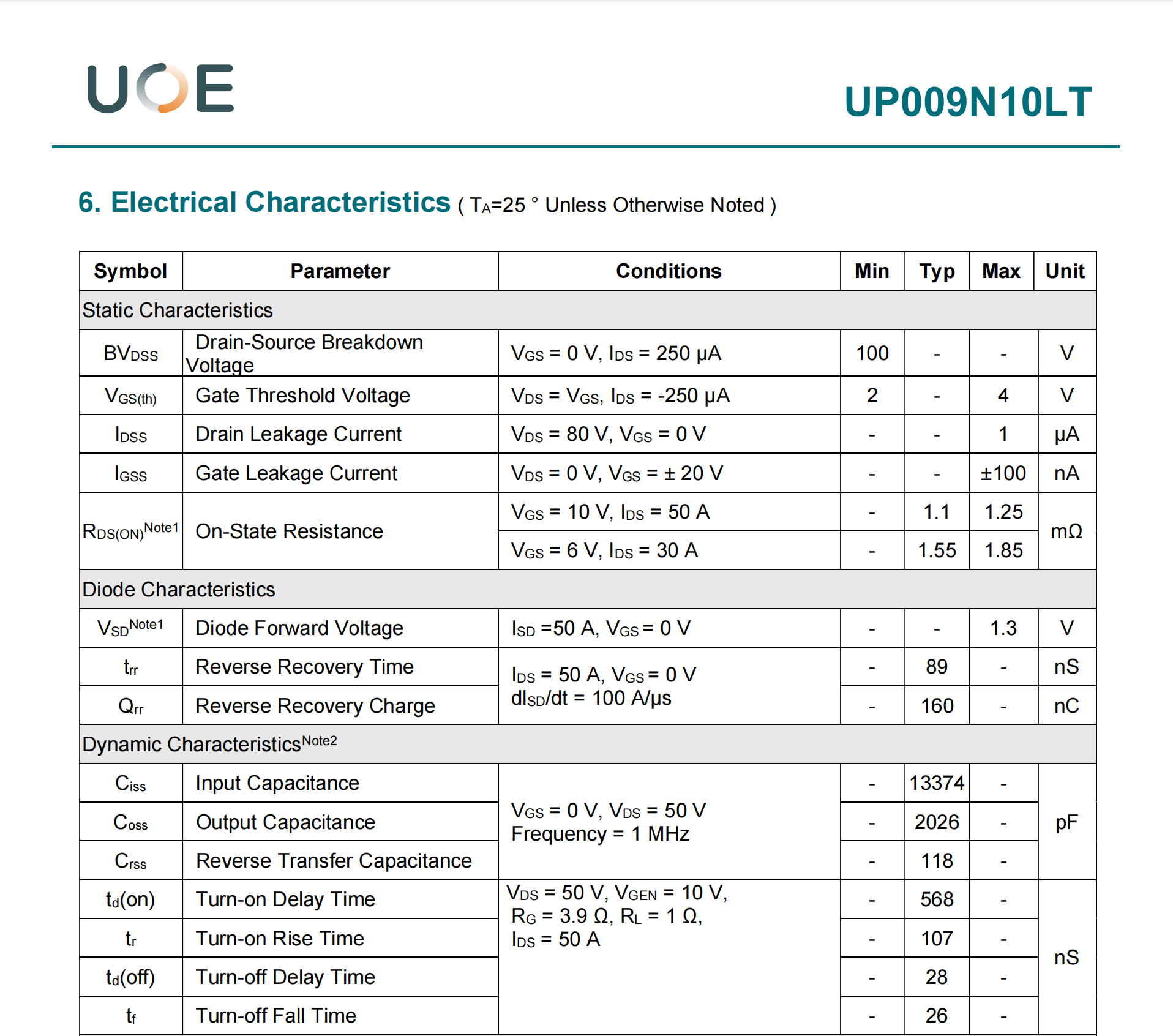

6です。電気パラメーターです

TOLTパッケージ内のMOSFETは、対応するTOLLコンポーネントと同じRDS(on)値を有します。例えば、采toltパッケージの優れた100 v mosfet (UP009n10lt)と相応のtoll (UP009n10t)、rds (on)、max均1.25 mオメガ。

TOLTの最大の改善点は、穴が開いた一般的な2s2p回路基板と周囲温度85°Cで、ヒートシンクに接続する熱抵抗Rthが著しく低下したことです。Rthは50%近く低下し、これにより総消費分散電力は90%以上向上します。

まとめです

新しい放熱TOLTパッケージは、高出力の工業用途のためにFR4 PCB上で実現します。TOLTはチューブコアからヒートシンクまでの熱経路を短縮することで熱抵抗を改善し,電気的性能を向上させます。